# Capacitance-Voltage Analysis for Al<sub>2</sub>O<sub>3</sub> based High-K Dielectric MOS Devices

Niladri Pratap Maity, A. K. Pandeya and Reshmi Maity

Department of Electronics & Communication Engineering, Mizoram University (A Central University) Aizawl-796004, India

#### Abstract

In this paper we have calculated Capacitance-Voltage (C-V) relationship for Metal Oxide Semiconductor (MOS) devices and plotted it for high-k dielectric material Aluminum Oxide  $(Al_2O_3)$  as oxide material, Si as substrate and compared it with conventional SiO<sub>2</sub> based MOS device. We have made the simplest possible model for the MOS device and based on it results have been derived. The C-V characteristics are also obtained from ATLAS simulator for the MOS. Excellent agreement has been observed for theoretical and simulation results for high frequency as well as low frequency C-V curve.

*Keywords:* C-V characteristics, High-k, Al<sub>2</sub>O<sub>3</sub>, MOS.

#### **1. Introduction**

Attempts are being made across the world to replace the conventional silicon di-oxide (SiO<sub>2</sub>) with different high-k dielectric materials. In this regard HfO<sub>2</sub> has got a lot of interest [1]. A wide study has been done on the alternative high-k dielectric materials [2]-[6]. Al<sub>2</sub>O<sub>3</sub> is also one of the good candidates for it [7]-[8]. This material can allow us to reduce the size of MOS devices because it would be able to withstand higher voltages for the same gate size. The thermodynamic stability of Al<sub>2</sub>O<sub>3</sub> is suitable, has high band gap energy, low leakage current and adequate value of dielectric constant. Further, Al<sub>2</sub>O<sub>3</sub> gate dielectrics displayed nearly same degradation rate of capacitance reduction as SiO<sub>2</sub> with increment of frequency, and preserved higher k quality better than SiO<sub>2</sub> over a very wide range of frequency [9]. In this paper, we have obtained the C-V relationship based on the simplest possible MOS model for the high-k dielectric material Al<sub>2</sub>O<sub>3</sub> and compared it for SiO<sub>2</sub>.

## 2. Theoretical Formulation

Using the relation between surface potential, space charge and electric field the capacitance-voltage characteristics have been derived for a MOS structure. The potential  $V_0$  is zero at the bulk of the semiconductor for a MOS device and at the semiconductor surface it is  $V_0 = V_{s_0}$  is the surface potential. The V<sub>0</sub> as a function of distance can be obtained from one dimensional Poisson's equation. At the bulk of a MOS Device the total space charge density  $\rho$  (x) and V<sub>0</sub> being zero, the resultant Poisson's equation [10] can be written as,

$$\frac{d^{W_{Q}}}{dx^{e}} = -\frac{q}{e} \{ \mathbb{E}_{ed} (e^{-\beta W_{Q}} - 1) - \mathbb{N}_{ed} (e^{\beta W_{Q}} - 1) \}$$

(1)

Where q is the charge of holes,  $P_{ed}$  and  $N_{ed}$  are the equilibrium densities for holes and electrons respectively at the bulk of a MOS device,  $\beta = q/kT$ , k is the Boltzman's Constant, T is the temperature and  $\varepsilon_s$  is the permittivity of the semiconductor. Putting the electric field,  $\xi = (-dV_0/dx)$  and integrating equation (1) toward the surface from the bulk of a MOS is,

$$\frac{u}{2}\xi^{\alpha} = -\frac{q}{\epsilon_{c}\beta} \left[ \mathbb{P}_{ed} \left( -e^{-\beta V_{0}} - \beta V_{0} + 1 \right) - \mathbb{N}_{ed} \left( e^{\beta V_{0}} - \beta V_{0} - 1 \right) \right]$$

<sup>(2)</sup>

Then we get,

$$\xi = \left(\frac{ekT}{q}\right) \sqrt{\left(\frac{qP_{ed}\beta}{ee_{a}}\right)} \left[ \left(e^{-\beta V_{0}} + \beta V_{0} - 1\right) + \frac{N_{ed}}{P_{ed}} \left(e^{\beta V_{0}} - \beta V_{0} - 1\right) \right]$$

(3)

Now at the surface the electric field becomes

$$\xi_s = \pm \frac{\sqrt{2kT}}{qL_p} C$$

Where  $L_D$  is the Debye Length for holes and C is a constant with function of  $\beta V_0$  and  $N_{ed} / P_{ed}$  and it is given by,

$$\mathbf{C} = \left[ \left( \mathbf{e}^{-\beta V_0} + \beta V_0 - 1 \right) + \frac{N_{ed}}{R_{ed}} \left( \mathbf{e}^{\beta V_0} - \beta V_0 - 1 \right) \right]^{1/2}$$

(5)

Now, from Gauss's law (or unit volume,  $\int dV = 1$ ) the space charge per unit area is

$$\mathbf{Q}_{\text{space}} = -\frac{\sqrt{2\alpha_{e}kT}}{\sqrt{16}} \sqrt{\left[6^{-\beta V_{0}} + \beta V_{0} - 1 + \frac{N_{ed}}{P_{ed}} \left(6^{\beta V_{0}} - \beta V_{0} - 1\right)\right]}$$

(6)

Where,  $\epsilon_s$  is the permittivity of the semiconductor for the device. Then the differential capacitance at the depletion layer of MOS is,

$$C_{D} = \frac{dQ_{gpace}}{dV_{0}} - \frac{\varepsilon_{0}}{\sqrt{2}L_{D}} \frac{\left((1 - e^{-\beta V_{0}}) + \frac{N_{ed}}{P_{ed}}(e^{\beta V_{0}} - 1)\right)}{C}$$

(7)

When a potential is applied across a MOS structure the charges in oxide and semiconductor layers align themselves so as to resemble a capacitor. Now the capacitance of the system depends upon the frequency of applied electric field. As pointed out earlier the capacitance of the oxide layer does not depend upon the applied potential and is fixed depending upon its dielectric permittivity and the geometry. But in the semiconductor layer the effective width over which the charges are there changes with applied potential. Depending upon the polarity of the applied potential either majority or minority charge carriers have to move towards the surface or away from it.

### 3. Result and Discussions

With external applied voltage the majority carriers can respond immediately but for minority carriers the response time is more. If the applied potential changes so quickly that the polarity across the MOS changes before the minority carriers could respond to the applied field, the applied field is said to have a high frequency. On the otherhand if minority charges carriers are able to respond to the applied field and then the polarity is changed then the frequency of the applied field is said to be low.

Let us consider a pMOS, try to understand what will happen by applying an AC voltage across MOS and obviously the arguments for nMOS will be exactly similar except to as the polarity of the applied bias and the nature of the majority and minority charge carriers. In the negative half cycle when the magnitude is sufficiently large the maximum possible majority charge carriers get accumulated near the oxide semiconductor surface and the capacitance reaches its maximum value. As the magnitude of the applied potential decreases, proportionally the accumulation decreases and there is no effect on the capacitance of the semiconductor layer. But as the magnitude of potential gets closer to zero, the mutual repulsion between the majority charge carriers also become important. And the accumulated charge decreases faster than the applied potential decreases. At zero applied potential still holes are there in majority and there is a finite capacitance. Now when the potential becomes positive majority charge carriers will be gradually repelled and the minority charge carriers come towards the surface.

These results in decrease in charge till both of them become equal in density near the surface. At this point the capacitance is a minimum. Now as the positive potential is increased further inversion begins to take place and capacitance increases. Finally it reaches its maximum value after which it remains constant. Now as we made the model for our low frequency electric field, we can claim that all the formula derived for the static potential case will be valid in this case too, except that the potential will vary with time. So our set of equations is,

$$C_{\rm D} = \frac{dQ_{\rm space}}{dV_{\rm 0}} = \frac{1}{2} \frac{\sqrt{2}e_{\rm s}kT}{qL_{\rm D}} \frac{\sqrt{[-\beta e^{-\beta V_{\rm s}} + \beta + \frac{N_{\rm sd}}{E_{\rm sd}}(\beta e^{\beta V_{\rm s}} - \beta)]}}{C}$$

(8)

The voltage applied across the MOS system distributes across the oxide layer and semiconductor i.e.

$$\mathbf{V}(t) = \mathbf{V}_{\mathbf{s}}(t) + \frac{\mathbf{Q}_{\mathbf{s}}}{\mathbf{C}_{\mathbf{I}}}$$

(9)

Now  $C_I$  is fixed because none of the parameters controlling it has changed but  $V_s$  changes with time. So  $C_D$  also changes because it is controlled by  $V_s$  and the net capacitance of the system also changes. So,

$$\frac{1}{C} = \frac{1}{C_{exc}} + \frac{1}{C_{D}} \Rightarrow \frac{C}{C_{exc}} = \frac{C_{U}}{C_{D} + C_{exc}}$$

(10)

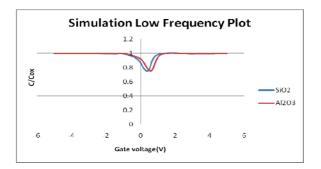

For  $SiO_2$  and  $Al_2O_3$  the low frequency behavior is plotted in figure 1.

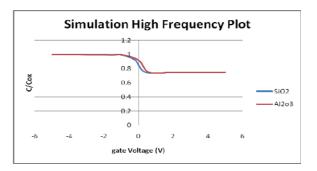

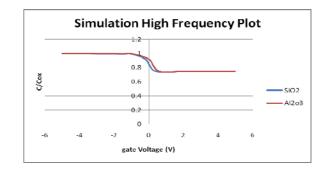

As already said high frequency would mean that minority carriers don't get sufficient time to do the best. Certainly if the frequency applied is so high that it doesn't even allow majority charge carriers to respond, then the following arguments and hence the derived equations won't be valid anymore. But by developing a mathematical model we can come to the conclusion that frequency till what we usually apply practically, majority charge carriers respond almost instantaneously. So the arguments till the minimum capacitance is reached remains the same as it was in the low frequency behavior (because it is decided by the majority charge carriers). After it since the minority carriers can't respond with changing rate of field there would not be any rise in the capacitance (see figure 2). Then the equations become:

Fig. 1 Low frequency curve.

Fig. 2 High frequency curve.

The change in relative capacitance of MOS with  $Al_2O_3$  as the gate material is for larger value of gate voltage than for MOS with SiO<sub>2</sub>. The transition region starts at more positive value of gate voltage than in SiO<sub>2</sub> based MOS. This is because of the capability of  $Al_2O_3$  to withstand more electric field as discussed earlier. Thus it can be said that the stability of MOS structure has increased.

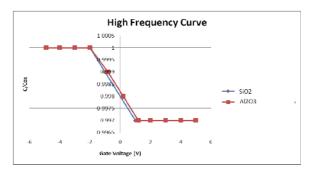

The MOS device with  $SiO_2$  and  $Al_2O_3$  as the oxide material, alternatively are modeled and simulated with ATLAS simulator for low frequency (see figure 3) as well as high frequency (see figure 4). The variation  $C/C_{ox}$  with the gate voltage as the independent parameter shows the some variation as obtained with the theoretical modeling of the MOS device used in this paper.

Fig. 3 Low frequency curve (simulated).

Fig. 4 High frequency curve (simulated).

The minimum capacitance of the simulated curve is less than that of the theoretical, which is due to the effect of the capacitance due to the fast interface charge density. That is incorporated by the simulated result, and appears in parallel combination with depletion capacitance at the insulator-semiconductor interface. Hence  $Al_2O_3$  is having a high-k value, the same electrical characteristics as that of a MOS device with  $SiO_2$  as the insulator material, can be obtained with a greater thickness of  $Al_2O_3$ , hence reducing the leakage current considerably.

## 4. Conclusions

The theoretical study revealed that even a very simple model can be used for the study of complex devices like MOS. Almost identical transitions in C-V are observed theoretically as well as simulation with the gate dielectric materials, showing better reliability of  $Al_2O_3$  with significant reduction of tunneling leakage current. The higher thickness of  $Al_2O_3$  also results in lesser leakage current. The only major problem is the interfacial property of the Si- $Al_2O_3$ .

#### Acknowledgments

The authors are highly indebted to Department of Science and Technology (DST), Ministry of Science and Technology, New Delhi, India for supporting this technical work.

#### References

- [1] S. Rhee, C. Y. Kang, C. S. Kang, R. Choi, C. H. Choi, M. S. Akbar, and J. C. Lee, "Effects of varying interfacial oxide and high-k layer thicknesses for HfO<sub>2</sub> metal-oxidesemiconductor field effect transistor", Appl. Phys. Letters, Vol. 85, 2004, pp. 1286-1288.

- [2] H-H. Hsu, Y. Chang, and J. Lee, "Metal-oxide-high-k dielectric-oxide-semiconductor (MOHOS) capacitors and field-effect-transistors for memory applications", IEEE Electron Device Letters, Vol. 28, 2007, pp. 964-966.

- [3] N. Sing, W. W. Fang, S. C. Rustagi, K. D. Budharaju, S. H. Teo, S. Mohanraj, G. Q. Lo, N. Balasubramanium, and D. L. Kwong, "Observation of Metal layer stress on Si Nanowires in Gate-All-Around high-k/ Metal-Gate device structures", IEEE Electron Device Letters, Vol. 28, 2007, pp. 558-561.

- [4] D. C. Suh, Y. D. Cho, S. W. Kim, D-H. Ko, Y. Lee, M-H. Cho, and J. Oh, "Improved thermal stability of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> high-k gate dielectric stack on GaAs", Appl. Phys. Lett., Vol. 96, 2010, pp. 142112-4.

- [5] R. G. Southwick, J. Reed, C. Buu, R. Butler, G. Bersuker, and B. K. Knowlton, "Limitations of Poole–Frenkel Conduction in Bilayer HfO<sub>2</sub>/SiO<sub>2</sub> MOS Devices", IEEE Transactions on Device Materials Reliability, Vol. 10, 2010, pp. 201-207.

- [6] Hang Hu, Chuxiang Zhu, Xiongfei Yu, Albert Chin, M. F. Li, M. F. Li, Byung Jin Cho, Dim Lee Kwong, P. D. Foo, Ming Bin Yu, Xyne Liu, and Jerry Wrinkler, "MIM capacitors using atomic-layer-deposited high-/spl kappa/ (HfO/sub 2/)/sub 1-x/(Al/sub 2/O/sub 3/)/sub x/ dielectrics", IEEE Electron Device Letters, Vol. 24, 2003, pp. 60-62.

- [7] Y. T. Hou, M. F. Li, H. Y. Yu, and D. L. Kwong, "Modeling of tunneling currents through HfO<sub>2</sub> and (HfO<sub>2</sub>)<sub>x</sub>(Al<sub>2</sub>O<sub>3</sub>)/sub 1-x/ gate stacks", IEEE Electron Device Letters, Vol. 24, 2003, pp. 96-98.

- [8] Y. Xuan, Y. Q. Wu, H. C. Lin, T. Shen, and P. D. Ye, "Submicrometer Inversion-Type Enhancement-Mode InGaAs MOSFET with Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> as Gate Dielectric", IEEE Electron Device Letters, Vol. 28, 2007, pp. 935-938.

- [9] S.B. Chen, C. H. Lai, K.T. Chan, Albert Chin, J. C. Hsieh, and J. Liu, "Frequency-dependent capacitance reduction in high-k AlTiO<sub>x</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics from IF to RF frequency range", IEEE Electron Device Letters, Vol. 23, 2002, pp. 203-205.

[10] S. M. Sze, Editor, Physics of Semiconductor Devices, New York: John Wiley & Sons Inc., 1981.

Niladri Pratap Maity received the M. Sc. Degree in Electronics from Sambalpur University and M. Tech. degree in Electronics Design & Technology from Tezpur University (A Central University, Govt. of India), India. He joined the Mizoram University (A Central University) as an Assistant Professor and Head of the Department of Electronics & Communication Engineering in 2007. He has good industrial experience in the field of VLSI design & Microelectronics. He is currently working with high-k dielectric materials, microelectronics and Electronics Materials. He is the author of more than 35 international journal/conference papers with a best paper award and an excellent paper award. He is the Life Member of Semiconductor Society of India (SSI), Indian Society of Technical Education (ISTE), Photonics Society of India (PSI) and Material Research Society of India (MRSI). He has got the Visiting Scientist Fellow Award from Department of Science & Technology (DST), Ministry of Science & Technology (MIT), Govt. of India in 2010. He is working with several ongoing major projects from Ministry of Human Resource & Development (MHRD) and Ministry of Information Technology, Govt. of India.

**A. K. Pandeya** is a last year student of Bachelor of Technology (B. Tech.) in Electronics & Communication Engineering of Department of Electronics & Communication Engineering, Mizoram University (A Central University). He is working the major project for his partial fulfillment of the B. Tech. degree.

**Reshmi Maity** received the B. Tech. and M. Tech. degree in Radio Physics & Electronics from University of Calcutta, Kolkata, India. She joined the Mizoram University (A Central University) as an Assistant Professor in the Department of Electronics & Communication Engineering in 2008. She has good teaching and research experience in the field of MEMS and Microelectronics. She is the author of more than 25 international journals / conferences.