# Design of a High Performance Reversible Multiplier

Md. Belayet Ali<sup>1</sup>, Hosna Ara Rahman<sup>2</sup> and Md. Mizanur Rahman<sup>3</sup>

<sup>1</sup>Department of Computer Science and Engineering, Mawlana Bhashani Science And Technology University, Tangail-1902, Bangladesh

<sup>2</sup>Department of Computer Science and Engineering, Mawlana Bhashani Science And Technology University, Tangail-1902, Bangladesh

<sup>3</sup>Department of Computer Science and Engineering, Mawlana Bhashani Science And Technology University, Tangail-1902, Bangladesh

#### Abstract

Reversible logic circuits are increasingly used in power minimization having applications such as low power CMOS design, optical information processing, DNA computing, bioinformatics, quantum computing and nanotechnology. The problem of minimizing the number of garbage outputs is an important issue in reversible logic design. In this paper we propose a new  $4 \times 4$  universal reversible logic gate. The proposed reversible gate can be used to synthesize any given Boolean functions. The proposed reversible gate also can be used as a full adder circuit. In this paper we have used Peres gate and the proposed Modified HNG (MHNG) gate to construct the reversible fault tolerant multiplier circuit. We show that the proposed 4×4 reversible multiplier circuit has lower hardware complexity and it is much better and optimized in terms of number of reversible gates and number of garbage outputs with compared to the existing counterparts.

**Keywords:** Reversible logic circuit, reversible logic gates, reversible multiplier circuits, quantum computing, nanotechnology based systems.

## 1. Introduction

Irreversible hardware computation results in power dissipation due to information loss. As demonstrated by R.Landauer in the early 1960s, irreversible hardware computation, regardless of its realization technique, results in energy dissipation due to the information loss[1]. According to his research,

the combinational logic circuits dissipate heat in an order of  $kT \ln 2$ joules of energy for every bit of information that is erased, where  $k=1.3806505 \times 10^{-10}$  $^{23}$  m<sup>2</sup> kg  $^{-2}$ k  $^{-1}$  (joules Kelvin  $^{1}$ ) is the Boltzman constant and T is the operating temperature [1]. For room temperature T the amount of dissipating heat is small(i.e.  $2.9 \times 10^{-21}$  joule), but not negligible. The design that does not result in information loss is called reversible. It naturally takes care of heating generated due to the information loss. Such gates or circuits allow the reproduction of the inputs from observed outputs and we can determine the inputs from the outputs [3] [4] [5]. Thus reversibility will become an essential property in future circuit design. Reversible logic has applications in various research areas such as low power CMOS design, optical computing, quantum computing, bioinformatics, thermodynamic technology, DNA computing and nanotechnology.

The difference of reversible logic synthesis compared to binary logic synthesis can be summarized as follows[8]:

- 1) The gates used to implement the circuit have the equal number of inputs and outputs.

- Every output of a gate, which is not used in the circuit, is a garbage signal. A good synthesis method minimizes the number of garbage signals.

- 3) The total number of constants at inputs of the gates is kept as low as possible.

- 4) A gate output can be used only once (the fanout count of each output is equal to one). If two copies of a signal are required, a copying circuit is used.

- 5) The resulting circuit is acyclic.

Any reversible gate performs the permutation of its input patterns only and realizes the functions that are reversible. If a reversible gate has k inputs, and therefore k outputs, then we call it a  $k \times k$  reversible gate. Any reversible circuit design includes only the gates that are reversible. A reversible circuit should have the following features [4]:

- 1) Use minimum number of reversible logic gates.

- 2) Use minimum number of garbage outputs.

- 3) Use minimum constant inputs.

Every output of a gate, which is not used for further computations, is a garbage signal[8]. The input that is added to an nxk function to make it reversible is called constant input [12]. In many computational units multiplication is a heavily used arithmetic operation. For the processors to have high speed multipliers is very important. In this paper, we present a reversible multiplier circuit using reversible MHNG gate. We demonstrate that proposed the reversible multiplier circuit is better than the existing counterparts in terms of number of gates, number of garbage outputs, number of constant inputs and hardware complexity [20] [21] [22] [23] [24].

## 2. Reversible Logic

The *n*-input *k*-output Boolean function  $f(x_1, x_2, ..., x_n)$  (referred to as (n, k) function) is called reversible if:

- 1) The number of outputs is equal to the number of inputs;

- 2) Each input pattern maps to a unique output pattern[13].

In other words, reversible functions are those that perform permutations of the set of input vectors.

## **3.** Reversible Logic Gates

An nxn reversible logic gate can be represented as:

$$I_{v} = (I_{1}, I_{2}, I_{2}, ..., I_{N})$$

$O_{v} = (O_{1}, O_{2}, O_{3}, ..., O_{N})$

Where  $I_v$  and  $O_v$  are input and output vectors respectively. Several reversible logic gates have been proposed in the past few decades. Some of them are: Feynman gate, FG [6], Toffoli gate, TG [7], Fredkin gate, FRG[15], Peres gate, PG [11], New Gate, NG [14], TSG gate, TSG [5], MKG gate, MKG [16] and HNG gate, HNG [18]. In this section we review these reversible logic gates. Some of them are presented to allow for comparison with existing studies.

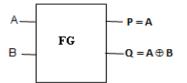

#### 3.1 Feynman gate (FG)

Feynman gate (FG), also known as controlled-not gate (1-CNOT), is a  $2\times 2$  gate that can be described by the equations:

$$I_v = (A, B)$$

$$O_v = (P = B, Q = A \oplus B)$$

where 'A' is control bit and 'B' is the data bit. It is shown in Fig. 1.

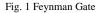

#### 3.2 Fredkin gate (FRG)

Fredkin gate (FRG), also known as controlled permutation gate, is a 3x3 reversible logic gate. It can be represented as:

$$I_v = (A, B, C)$$

$$O_v = (P = A, Q = A'B \oplus AC, R = A'C \oplus AB)$$

Where  $I_v$  and  $O_v$  are input and output vectors. It is shown in Fig. 2. Fredkin Gate is a conservative gate, that is, the Hamming weight of its input vector is the same as the Hamming weight of its output vector.

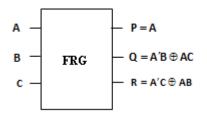

#### 3.3 Toffoli gate (TG)

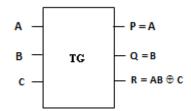

Toffoli gate (TG), also known as controlled controlled-not (CCNOT), is a 3x3 reversible logic gate. The Toffoli gate can be represented as:

$$I_v = (A, B, C)$$

$$O_v = (P = A, Q = B, R = AB \oplus C)$$

Where  $I_v$  and  $O_v$  are input and output vectors. The Toffoli gate is shown in Fig. 3.

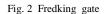

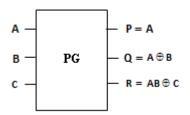

3.4 Peres gate (PG)

Peres gate (PG), also known as New Toffoli Gate(NTG), combining Toffoli gate and Feynman gate is a 3x3 reversible logic gate. It can be represented as:

$$I_v = (A, B, C)$$

$$O_v = (P = A, Q = A \oplus B, R = AB \oplus C)$$

Where  $I_v$  and  $O_v$  are the input and output vectors. The Peres gate is shown in Fig. 4. Peres gate is equal with the transformation produced by a Toffoli Gate followed by a Feynman Gate.

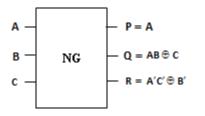

3.5 New gate (NG)

New gate (NG), is a 3x3 reversible gate. It can be represented as:

$$I_v = (A, B, C)$$

$$O_v = (P = A, Q = AB \oplus C, R = A'C' \oplus B')$$

Where  $I_v$  and  $O_v$  are the input and output vectors. The New gate is shown in Fig. 5.

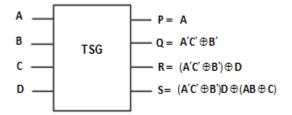

## 3.6 TSG gate

TSG gate is a  $4\times4$  reversible gate. The TSG gate is shown in Fig. 6., where each output is annotated with the corresponding logic expression:

$I_v = (A, B, C, D)$   $O_v = (P = A, Q = A'C' \oplus B, R = (A'C' \oplus B') \oplus D,$  $S = (A'C' \oplus B') D \oplus (AB \oplus C))$

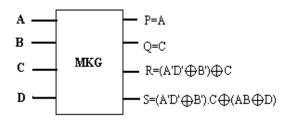

#### 3.7 MKG gate

MKG gate is a 4x4 reversible logic gate. The MKG gate can be represented as:

$$\begin{split} I_v &= (A, B, C, D) \\ O_v &= (P = A, Q = C, R = (A'D' \oplus B') \oplus C, \\ S &= (A'D' \oplus B').C \oplus (AB \oplus D)) \end{split}$$

Where  $I_v$  and  $O_v$  are the input and output vectors. The MKG gate is shown in Fig. 7., where each output is annotated with the corresponding logic expression.

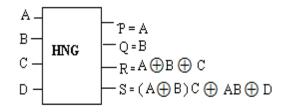

#### 3.8 HNG gate

The HNG gate is universal. The HNG gate is shown in Fig.8., where each output is annotated with the corresponding logic expression. The corresponding logic expression of HNG gate:

$$I_v = (A, B, C, D)$$

$$O_v = (P = A, Q = B, R = A \oplus B \oplus C,$$

$$S = (A \oplus B).C \oplus AB \oplus D)$$

www.IJCSI.org

Fig. 5 New Gate

Fig. 6 TSG Gate

Fig. 7 Reversible MKG Gate

Fig. 8 Reversible HNG Gate

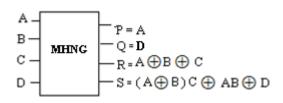

Fig. 9 Reversible MHNG Gate

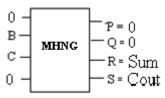

### 4. Proposed Modified HNG Gate

Our proposed Modified HNG (MHNG) gate is a 4×4 reversible logic gate. The corresponding logic expression of MHNG gate:

$$I_v = (A, B, C, D)$$

$$O_v = (P = A, Q = D, R = A \oplus B \oplus C,$$

$$S = (A \oplus B).C \oplus AB \oplus D)$$

Where,  $I_v$  and  $O_v$  are the input and output vectors. The MHNG gate is shown in Fig.9, where each output is annotated with the corresponding logic expression.

The corresponding truth table of the MHNG gate is depicted in Table 1.

| Table 1: Truth Table for Proposed | Reversible MHNG gate |

|-----------------------------------|----------------------|

|-----------------------------------|----------------------|

| A | B | С | D | P | Q | R | S |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | Õ | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

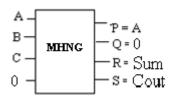

One of the prominent functionalities of the MHNG gate is that it can work singly as a reversible full adder unit. If  $I_v = (A, B, C_{in}, 0)$ , then the output vector becomes:  $O_v=(P=A, Q=0, R=Sum, S=C_{out})$ . Therefore, we have both of the required outputs. Implementation of the MHNG gate as the reversible full adder is shown in Fig. 10. The proposed reversible full adder circuit uses only one reversible logic gate. It produces only two garbage outputs. It requires only one constant input.

Let,

a = A two input EX-OR gate calculation  $\beta = A$  two input AND gate calculation

For [5]: T=6a+3B+3d, for [16]: T=5a+3B+3d, for [18]: T=5a+2B and for proposed MHNG gate : T=5a+2B. Thus, the proposed reversible full adder is better than the reversible full adder circuits in [5,16,18] in term of hardware complexity.

MHNG gate also performs as reversible half adder. If  $I_v = (0, B, C_{in}, 0)$ , then the output vector becomes:  $O_v=(P=0, Q=0, R=Sum, S=C_{out})$ . Implementation of the MHNG gate as the reversible half adder is shown in Fig. 11.

Fig. 10 MHNG Full Adder

Fig. 11 MHNG half Adder

We will use MHNG gates to construct the novel reversible multiplier circuit.

## 5. Reversible Multiplier Circuit

The operation of the 4x4 multiplier is depicted in Fig. 12. It consists of 16 partial product bits of the form  $x_i.y_i$ . The proposed reversible 4x4 multiplier circuit has two parts. First, the partial products are generated in parallel using Toffoli and Peres gates [23]. Then, the addition is performed as shown in Fig. 13.

The basic cell for such a multiplier is a full adder (FA) accepting three bits. We use MHNG gates as reversible full adder which is depicted in Fig. 10. The proposed reversible multiplier circuit uses eight reversible MHNG full adders. In addition, it needs four reversible half adders. It is possible to use MHNG gate as half adder, but we use Peres gate as reversible half adder because it has less hardware complexity compared to the MHNG gate.

### 6. Evaluation of Reversible Multiplier Circuit

The proposed reversible multiplier circuit is more efficient than the existing circuits presented in [19] [20] [21] [22] [23] [24]. Evaluation can be comprehended easily with the help of the comparative results in Table2. One of the main factors of a circuit is its hardware complexity. We can prove that our proposed circuits are better than the existing approaches in term of hardware complexity.

Let,

a = A two input EX-OR gate calculation  $\beta = A$  two input AND gate calculation d = A NOT calculation T = Total logical calculation

|                       |                               | х              |                                                         |                                                 | x <sub>2</sub><br>y <sub>2</sub> | -              | х <sub>0</sub><br>Уо          |

|-----------------------|-------------------------------|----------------|---------------------------------------------------------|-------------------------------------------------|----------------------------------|----------------|-------------------------------|

|                       | x <sub>3</sub> y <sub>3</sub> |                | $\begin{array}{c} x_3y_1\\ x_2y_2\\ x_1y_3 \end{array}$ | $\begin{array}{c} x_2y_1 \\ x_1y_2 \end{array}$ | •                                | •              | x <sub>0</sub> y <sub>0</sub> |

| <b>P</b> <sub>7</sub> | P <sub>6</sub>                | P <sub>5</sub> | $P_4$                                                   | P <sub>3</sub>                                  | P <sub>2</sub>                   | P <sub>1</sub> | P <sub>0</sub>                |

Fig. 12 Partial products in a 4x4 multiplication

For [19] the Total logical calculation is:T=80a+100B+68d, for [20] the Total logical calculation is: T=110a+103B+71d, for [21] the Total logical calculation is: T=92a+52B+36d ,for [22] the Total logical calculation is: T=80a+36B, for [23] the Total logical calculation is: T=71a+36B, for [24] the Total logical calculation is: T=71a+35B, and for our proposed reversible multiplier circuit, the Total logical calculation is: T=80a+36B. Therefore, the proposed reversible multiplier circuit is better than the existing circuits[19][20][21] in term of complexity.

Our proposed reversible  $4 \times 4$  multiplier circuit is shown in Fig.13. We used eight reversible MHNG full adders and four reversible half adders.

In the proposed reversible multiplier circuit we use MHNG gate as reversible full adder and it produces zero (0) in second output, which we have used as the fourth input for the next MHNG full adder circuit. Thus this proposed reversible  $4\times4$  multiplier circuit produces less garbage outputs than the existing counterparts in [19]-[24].

Fig. 13 Proposed 4x4 reversible multiplier circuit using MHNG gates and Peres gates.

| Table 2: Comparative | Experimental | Results | of | Different | Reversible |

|----------------------|--------------|---------|----|-----------|------------|

| Multiplier Circuits. |              |         |    |           |            |

| Paper<br>No. | No. of<br>Gates | No. of<br>Garbage<br>Outputs | No. of<br>Constant<br>Inputs | Total Logical<br>Calculation |

|--------------|-----------------|------------------------------|------------------------------|------------------------------|

| This         | 28              | 22                           | 28                           | 80a+36ß                      |

| Work         |                 |                              |                              |                              |

| [24]         | 28              | 32                           | 28                           | 71a+35ß                      |

| [23]         | 28              | 28                           | 28                           | 71a+36ß                      |

| [22]         | 28              | 52                           | 28                           | 80a+36ß                      |

| [21]         | 28              | 56                           | 32                           | 92a+52ß+36d                  |

| [20]         | 29              | 58                           | 34                           | 110a+103ß+71d                |

| [19]         | 40              | 56                           | 31                           | 80a+100ß+68d                 |

#### 7. Results and Discussion

The proposed reversible multiplier circuit is more efficient then the existing circuit presented in [19] – [24]. Evaluation of proposed circuit can be comprehended

easily with the help of the comparative results in Table 2. The difference between partial products generation design with the existing designs in [19, 20, 21, 22, 24] is the use of Toffoli gates and Peres gates. This structure is proposed in [23]. This design method of generating partial product has less hardware complexity. Therefore, the proposed reversible multiplier circuit is better than the existing circuits in terms of complexity.

One of the other major constrains in designing a reversible logic circuit is less number of garbage output, but the design in [19] produces 56 garbage outputs, the design in [20] produces 58 garbage outputs, the design in [21] produces 56 garbage outputs, the design in [22] produces 52 garbage outputs, the design in [23] produces 28 garbage outputs, the design in [24] produces 32 garbage So, we can state that our design approach is better than all the existing counterparts in term of number of garbage outputs.

Number of constant inputs is one of the other main factors in designing a reversible logic circuit. Our proposed reversible multiplier circuit requires 28 constant inputs, but the [19] requires 31 constant inputs, the design in [20] requires 34 constant inputs, the design in [21] requires 32 constant inputs, the design in [23] requires 28 constant inputs.

Comparing our proposed reversible multiplier circuit with the existing circuits in [19]- [24], it is found that the proposed design approach requires 28 reversible logic gates but the existing design in [19] requires 40 reversible gates, the existing design in [20] requires 29 reversible gates, the existing design in [21] requires 28 reversible gates, the existing design in [22] requires 28 reversible gates, the existing design in [23] requires 28 reversible gates and the existing design in [24] requires 28 reversible gates. So, the proposed circuit is better than [19] [20] [21] [22][23][24] in term of number of reversible logic gates, which is one of the other main factors in reversible circuit design.

From the above discussion we can conclude that the proposed reversible multiplier circuit is better than all the existing design.

## 8. Conclusions

In this paper, we presented a 4x4 bit reversible multiplier circuit using MHNG gates, Toffoli gates and Peres gates. Table II demonstrates that the proposed reversible multiplier circuit is better than the existing designs in terms of hardware complexity, number of logic gates, garbage outputs, constant inputs and optimized in terms of area and delay time. Our proposed reversible multiplier circuit can be applied to the design of complex systems in nanotechnology.

## References

- [1] Landauer, R., 1961. Irreversibility and heat generation in the computing process", IBM J.Research and Development, 5(3): 183-191.

- [2] C. H. Bennet, "Logical reversibility of computation", IBM J. Res. Develop., vol. 17, no. 6, pp. 525-532, 1973.

- [3] M. Perkowski, A. Al-Rabadi, P. Kerntopf, A. Buller, M. Chrzanowska-Jeske, A. Mishchenko, M. Azad Khan, A. Coppola, S. Yanushkevich, V. Shmerko and L. Jozwiak, "A general decomposition for reversible logic", Proc. RM 2001, Starkville, (2001) pp. 119-138.

- [4] Perkowski, M. and P. Kerntopf, 2001. "Reversible Logic. Invited tutorial", Proc. EURO-MICRO, Sept 2001, Warsaw, Poland.

- [5] Thapliyal Himanshu and M. B. Srinivas, 2005. "Novel reversible TSG gate and its application for designing reversible carry look ahead adder and other adder architectures." Proceedings of the 10<sup>t</sup>thAsia-Pacific Computer Systems Architecture Conference (ACSAC 05), Lecture Notes of Computer Science, 3740: 775-786. Springer-Verlag.

- [6] Feynman, R., 1985. "Quantum mechanical computers", Optics News, 11: 11-20.

- [7] Toffoli T., 1980. "Reversible computing", TechMemo MIT/LCS/TM-151. MIT Lab for Computer Science.

- [8] Alan Mishchenko and Marek Perkowski, "Logic Synthesis of Reversible Wave Cascades", Portland Quantum Logic Group, Department of Electrical and Computer Engineering, Portland State University, Portland, OR 97207, USA.

- [9] M. Haghparast and K. Navi, "A novel fault tolerant reversible gate for Nanotechnology based systems", Am. J. of App. Sci., vol. 5, no.5, pp. 519-523,2008.

- [10] M. Haghparast and K. Navi, "Design of a novel fault tolerant reversible full adder for nanotechnology based systems", World App. Sci. J., vol. 3, no. 1, pp. 114-118,2008.

- [11] Peres, A., 1985. "Reversible logic and quantum computers", Physical Review: A, 32(6): 3266-3276.

- [12] Saiful Islam, M.D. and M.D. Rafiqul Islam, 2005.

"Minimization of reversible adder circuits". Asian J.Inform. Tech., 4 (12): 1146 1151.

- [13] Dmitri Maslov and Gerhard W. Dueck, "Garbage in Reversible Designs of Multiple Output Functions", University of New Brunswick, Fredericton, N.B. E3B 5 A3,CANADA.

- [14] Azad Khan, Md.M.H., 2002. "Design of full adder with reversible gate". International Conference on Computer and Information Technology, Dhaka, Bangladesh, pp: 515-519.

- [15] E. Fredkin and T. Toffoli, "Conservative logic", Intl. Journal of Theoretical Physics, pp. 219-253,1982.

- [16] M. Haghparast and K. Navi, "A Novel Reversible Full Adder Circuit for Nanotechnology Based Systems", Journal of Applied Sciences, 7 (24) (2007) 3995-4000.

- [17] M. Haghparast and K. Navi, "A Novel Fault Tolerant Reversible Gate For Nanotechnology Based Systems", American Journal of Applied Sciences, 5 (5) (2008) 519-523.

- [18] M. Haghparast and K. Navi, "A Novel reversible BCD adder for nanotechnology based systems", American Journal of Applied Sciences, 5 (3) (2008) 282-288.

- [19] Thaplyal, H., M.B. Srinivas and H.R. Arabnia, 2005. "A Reversible Version of 4x4 Bit Array Multiplier With Minimum Gates and Garbage Outputs", The 2005 International Conference on Embedded System and Applications (ESA'05), Las Vegas, USA, pp: 106-114.

- [20] Thaplyal, H. and M.B. Srinivas, 2006. "Novel Reversible Multiplier Architecture Using Reversible TSG gate". *IEEE* international Conference on Computer Systems and Applications, pp: 100-103.

- Shams, M., M. Haghparast and K. Navi, 2008. "Novel Reversible Multiplier Circuit in Nanotechnology". World Appl. Sci. J., 3 (5): 806-810.

- [22] Hagharast.M, jafarali . S, Navi. K, Hashemipour. O,2008, "Design of a Novel reversible Multiplier circuit using HNG gate in Nanotechnology", World Applied Sciences. J., 3(6): 974-978.

- [23] M. Haghparast, M. Mohammadi, K.Navi, M.Eshghi, "Optimized reversible multiplier circuit", Journal of Circuits, Systems, and Computers, World Scientific Publishing Company.

- [24] Nidhi Syal, Dr. H.P. Sinha, "High performance reversible parallel multiplier", International Journal of VLSI & Signal processing applications, Vol.1, Issue 3, (21-26), ISSN 2231-3133.

## **Biographical notes:**

**Md. Belayet Ali.** received his B.Sc degree in Computer Science and Engineering from Mawlana Bhashani Science and Tecgncehnology University, Santosh, Tangail, Bangladesh, in 2008. He is working as Lecturer in Department of Computer Science and Engieering at Mawlana Bhashani Science and Technology University (MBSTU), Santosh, Tangail, Bangladesh. He has 1 year experience of working in MBSTU. He has published 03(three) papers in national, international journals. His area of interest includes reversible logic synthesis, multi-valued reversible logic synthesis, network business security, cloud computing.

**Hosna Ara Rahman.** is currently completing her B.Sc degree in Computer Science and Engineering at Mawlana Bhashani Science and Technology University, Santosh, Tsangail, Bangladesh. Her area of interest include reversible logic synthesis.

**Md. Mizanur Rahman.** is currently completing his B.Sc degree in Computer Science and Engineering at Mawlana Bhashani Science and Technology University, Santosh, Tsangail, Bangladesh. His area of interest include reversible logic synthesis.