# Proposed Active Noise control System by using FPGA

Ahmad Sinjari<sup>1</sup>, Rafid A. Amory<sup>2</sup>, Rashad A. Alsaigh<sup>3</sup>

<sup>1</sup> Electrical Engineer, Salahuddin University, Collage of Engineering Erbil ,, Iraq

<sup>2</sup> Electrical Engineer, Mosul University, Collage of Engineering Mosul ,, Iraq

<sup>3</sup> Electrical Engineer, Mosul University, Collage of Engineering Mosul ,, Iraq

Abstract

This paper proposed active noise control (ANC) system by using field programmable gate array (FPGA) kit, it has been conducted through least mean square (LMS) algorithm in very high speed hardware description language (VHDL) code to control the noise.

Controlling the noise is of vital importance in the industrial field as the Acoustic noise has to be controlled due to work safety standards.

**Keywords:** LMS algorithm, ANC system, FPGA, adaptive filter.

#### 1. Overview

Acoustic noise has become a serious problem as the number of industrial equipment such as engines, blowers, fans, compressors and transformers are increased. The passive instruments such as enclosure or barrier for acoustic noise control have high attenuation over a broad frequency range. [1] The traditional approach to acoustic noise control uses passive techniques such as enclosures, barriers, and silencers to attenuate the undesired noise. [2], [3]. These passive silencers are valued for their high attenuation over a broad frequency range; however, they are relatively large, costly, and ineffective at low frequencies. Mechanical vibration is another related type of noise that commonly creates problems in all areas of transportation and manufacturing, as well as with many household appliances. [4]

In active noise control (ANC) systems, it is possible to limit the noise to a certain limit or even enhance noise to improve the sound quality of noise. Target spectra for the engine sound may be predetermined at different engine speeds. Target values can also be dependent on engine load or gear, for example. [5]

A review about ANC system is made in this paper which is structured as follows: section 2 introduces related work, section 3 present the design of the ANC system, section 4 describes the adaptive filter, section 5 describes the LMS algorithm, section 6 describe why we use FPGA, section 7 includes the proposed work, section 8 present the method of implementation of ANC, section 9 Proposed method, and section 10 includes Conclusions.

### 2. Related work

Various techniques and algorithm have been proposed for better active noise control system to reduce the noise in the field. Rafid A. and Aws H. (2008) present hardware implementation of least mean square (LMS) adaptive filter based Adaptive Noise Canceller (ANC) structure on FPGA using VHDL hardware description language. First, the adaptive parameters are obtained by simulating ANC on MATLAB. Second, the data, processed by FPGA, such as step size, input and output signals, desired signal, and coefficients of ANC, are exactly expressed into fixed-point data representation. Finally, the functions of FPGA-based system structure for such LMS algorithm in time sequence are synthesized, simulated, and implemented on Xilinx XC3S500E FPGA using Xilinx ISE 9.2i developing tool. The research results show that it is feasible to implement, on chip train, and use adaptive LMS filter based ANC in a single FPGA chip. [6]

Wolfgang F., Jörn M. and Bernd S. (2009) presented the FPGA-based system that suitable for augmented reality audio applications. The system consists of a Spartan -3 FPGA XC3S400 board connected to a Philips Stereo-

Audio- Codec UCB 1400. The algorithms for the FIR filtering and for the adaption of the filter coefficients according to the Widrow-Hoff LMS algorithm are implemented on the FPGA board.

Measurement results obtained with a dummy head measuring system are reported, and a detailed analysis of system performance and possible system improvements is given. [7]

Jerin K. (2012) presents hardware implementation of LMS adaptive filter based ANC structure on FPGA using VHDL hardware description language. First, the adaptive parameters are obtained by simulating ANC on MATLAB. Second, the data, Processed by FPGA, such as step size, input and output signals, desired signal, and coefficients of ANC, are exactly expressed into fixed-point data representation. Finally, the functions of FPGA-based system structure for Such LMS algorithm in time sequence are synthesized, simulated, and implemented on Xilinx XC3S500E FPGA using Xilinx ISE 9.2i developing tool. The research results show that it is feasible to implement, on chip train, and use adaptive LMS filter based ANC in a single FPGA chip. **[8]**

Saravanan V. (2013) is making a modification in the existing FxLMS algorithm that provides a new structure for improving the tracking performance and convergence rate based on the secondary path modeling technique. The convergence rate is improved by the dynamically varying the step size of the error signal. It is also implemented using FPGA. [9]

#### 3. Active Noise Control (ANC) system

Active noise control (ANC) involves an electro acoustic or electromechanical system that cancels specifically. Since the acoustic noise source and the environment are time varying, the characteristics of the undesired noise such as frequency content, the amplitude, phase, and the sound velocity are non-stationary. An ANC system must therefore be adaptive in order to cope with these variations. Adaptive filters adjust their coefficients for minimizing an error signal and are realized as the finite impulse response (FIR), the infinite impulse response (IIR), the lattice, and the transform-domain filters [2].

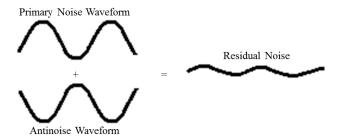

The noise cancellation depend on acoustically combine of unwanted sound and the anti-noise. Fig (1) shows the waveforms of the unwanted noise (the primary noise), the canceling noise (the anti-noise), and the residual noise that results when they superimpose. **[10]**

# Fig (1) The waveforms of the unwanted noise, the canceling noise (the anti-noise), and the residual noise

The success of an ANC system depends mainly on fulfilling two criteria:

- First, the anti-noise waveform must closely match the shape and frequency of the noise waveform.

- Second, the anti-noise wave must be precisely 180 degrees out of phase with respect to the original noise waveform, when reached to the target area.

Failure to fulfill one or both of these criteria may cause the ANC system to generate a second acoustic noise rather than cancel the original one.

### 4. Adaptive Noise Control: Basic Concepts

For the past many years, adaptive filters design has been an active area of scholarly research and innovative implementations.

An adaptive filter is a filter that self-adjusts its transfer function according to an optimization algorithm driven by an error signal. Because of the complexity of the optimization algorithms, most adaptive filters are digital filters. **[11]**

Adaptive filters are usually designed as FIR filters due to the fact that these filters are always stable and robust against parameter variations.

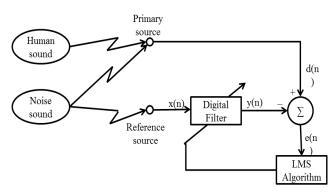

The goal of the system is to control the disturbing noise without affecting other sounds. For this purpose an adaptive feed forward system has to be stated. The basic system structure is given in fig (2): The primary signal d(n) consists of the superposition of noise signal s(n) and the wanted signal n(n). The reference signal x(n) is noise signal measured at the noise source. The system output signal y(n) is an estimate of the noise signal with inverted sign. The error signal e(n) is the result of a superposition process. If the adaptive filter does properly model the transmission path from the noise source to the error

microphone, the contribution of the noise signal to the error signal is minimised. This goal is achieved by minimising the mean square of the error signal (MSE adaption).

Fig (2) The basic system structure of adaptive noise system

### 5. LMS algorithm

One of the popular algorithms in the adaptive signal processing is the least mean square (LMS) algorithm which is widely analyzed in the literature, and a large number of results on its steady state misadjustment and its tracking performance are obtained.

The LMS algorithm was devised by Widrow and Hoff in 1959 in their study of a pattern-recognition machine known as the adaptive linear element, commonly referred to as the Adaline.

The LMS algorithm is a stochastic gradient algorithm in that it iterates each tap weight of the transversal filter in the direction of the instantaneous gradient of the squared error signal with respect to the tap weight in question. [12] Although the LMS filter is very simple in computational terms, its mathematical analysis is profoundly complicated because of its stochastic and nonlinear nature.

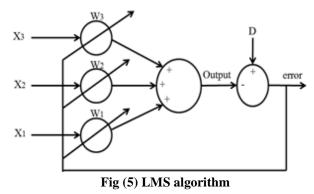

The procedure of the LMS algorithm can be described in three steps:

First step, calculate the output from the adaptive filter Second step, calculate the error signal by e(n)=d(n)-y(n)Third step, update the filter coefficients by  $W_{(n+1)}=W_{(n)}+\mu^*e_{(n)}^*u_{(n)}$

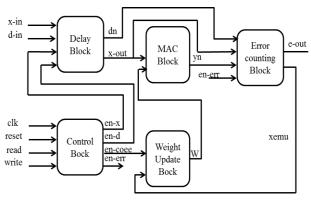

The LMS core is divided into five blocks, Control Block, Delay Block, Multiply Accumulator (MAC) Block,

Error Counting Block, and Weight Update Block as shown in fig (3)

Fig (3) The LMS core

# 6. Field Programmable Gate Array (FPGA) kit

The majorities of FPGAs are SRAM-based and can therefore be programmed as easily as standard SRAM. Because they are SRAM based, FPGAs are volatile. As such, they must be programmed each time power is applied. This is normally accomplished with another part of the circuit that reloads the configuration bit stream, such as a PROM. [13]

The Spartan®-3 Generation of FPGAs offers a choice of five platforms, each delivering a unique cost-optimized balance of programmable logic, connectivity, and dedicated hard IP for your low-cost applications.

## Spartan-3E - Logic Optimized

- For applications where logic densities matter more than I/O count

- Ideal for logic integration, DSP co-processing and embedded control, requiring significant processing and narrow or few interfaces

# 7. The method of implementation of ANC system

There are basically two ways in implementing ANC, an analog approach, and a digital approach.

# A. Analog Domain

As a technology, Analog technology is the process of translating the audio or video signal into electronic pulses.

This technology has been around for decades. It's not that complicated approach and it's fairly inexpensive to use. But, analog signals have size limitations as to how much data they can carry.

The simplest way to build up an ANC circuit is using an op-amp 741 IC.

The main disadvantage of analog technology is it leads to delay in superimposing the two signals, because it is a slow processing technology.

# **B. DIGITAL DOMAIN**

Digital technology is the process of breaking the signal into a binary format where the audio or video data is represented by a series of "1"s and "0"s.

The Digital technology can correct any errors that may have occurred in the data transfer, because it knows what it should be when it reaches the end of the transmission. The digital domain has a different ways of building an ANC circuit, they are by using:

### • Microcontroller

Microcontrollers are very small and somewhat versatile so they are special types of processor chips, due to their programmable nature. This type of processor is fully integrated. We can build ANC circuit using microcontroller with ADC & DAC circuits.

The delay occurs in super positioning of the original and the inverted signal, but still the processing speed is somewhat greater than using an op-amp.

## • Digital Signal Processor (DSP)

Digital signal processing allows the audio or video to be recorded and transmitted in ways not possible through previously used analog technology.

DSP is designed with signal processing in mind with extra multipliers and pipelines to allow faster signal processing, Programming a DSP is similar to programming any other type of microcontroller.

# • Field Programmable Logic Array (FPGA)

Major problem in the system of implementation can be resolved by use of modes in the system. Most of the environmental can be simulated by this method.

The noise control needs a high degree of speed and accuracy of operation, so we can use the FPGA to implement the ANC systems to achieve these parameters.

### 8. Proposed method

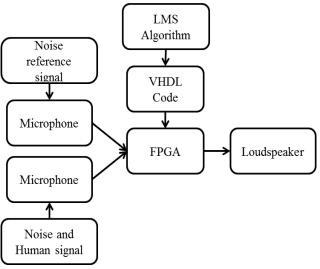

The proposed method is based on how to control the noise in the field using FPGA, the hardware description language called VHDL is used to make a control on FPGA, The code is written in a VHDL and it is simulated in Xilinx ISE 12.1.

The FPGA receives the two signals and processes them using the LMS algorithm by the VHDL code to result in the output to the loudspeaker as shown in Fig.(4).

Fig (4) The project flow.

LMS algorithm three sequenced inputs sounds (noise references); one at current moment and the two preceding signals as shown in fig (5).

The sum of these three signals after multiplying each by its coefficient (W) then subtracting the desired signal (noise and human) results in error, after a lot iteration, yield in the sound of human without noise.

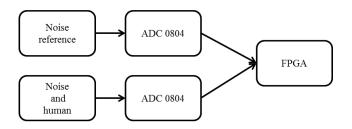

At first, An analog to digital chip (ADC) is used to convert the signal from analog to digital type because the Spartan 3-e kit need a digital signal from the noise signal with the human and noise signal on the other hand as shown in fig (6).

The Available ADC chip turned out to be too slow to convert the signal leading to new noise in the system. Therefore, the ADC is not fit enough to control the noise.

Fig (6) conversion the signal from analog to digital type

To overcome the previous problems, the Arduino Due is used which is a microcontroller board based on the Atmel SAM3X8E ARM Cortex-M3 CPU. It is the first Arduino board based on a 32-bit ARM core microcontroller. It has 54 digital input/output pins (of which 12 can be used as PWM outputs), 12 analog inputs, 4 UARTs (hardware serial ports), a 84 MHz clock, an USB OTG capable connection, 2 DAC (digital to analog), 2 TWI, a power jack, an SPI header, a JTAG header, a reset button and an erase button.

The Due has 12 analog inputs, each of which can provide 12 bits of resolution (i.e. 4096 different values). By default, the resolution of the readings is set at 10 bits, for compatibility with other Arduino boards. It is possible to change the resolution of the ADC with analog Read Resolution().

The digital to analog pins provides true analog outputs with 12-bits resolution (4096 levels) with the <u>analog</u> <u>Write()</u> function.

### 9. Conclusions

After a thorough study of ANC system and its filters, we found the benefits of using the LMS algorithm in the industrial field over other techniques in this field, where it proved its ability by testing many of the real problems.

In this paper an ANC system is proposed to control the noise by using LMS algorithm, which is implemented in Spartan 3-e.

The Spartan 3-e did not have an analog input pin, so we proposed to use the Arduino due as an analog to digital converter to enter the sound signal to the Spartan 3-e because of the speed of the Arduino due.

#### **References:**

- [1] Jalali A., Gholami Sh., and Eshghi M., "Design and Implementation of a Fast Active Noise Control System on FPGA", proceeding of the 15<sup>th</sup> Mediterranean Conference on Control & Automation, Athens – Greece, 2007.

- [2] Harris C., "Handbook of Acoustical Measurements and Noise Control", 3rd ed., New York: McGraw-Hill, 1991.

- [3] Beranek L., and Ver I., "Noise and Vibration Control Engineering: Principles and Applications", New York: Wiley, 1992.

- [4] Sen M., And Dennis R., "Active Noise Control: A Tutorial Review", Proceeding of the IEEE, Vol. 87, No. 6, June 1999.

- [5] Antti L., "Simulation Model for an Active Noise Control System Development and Validation", Master's Thesis, Master of Science in Technology, Helsinki University of Technology, 2008.

- [6] Rafid A., Aws H., "FPGA Implementation of Adaptive Noise Canceller", Al-Rafidain Engineering, Vol.17 No.4, 2009.

- [7] Wolfgang F., Jörn M., Bernd S., "A FPGA-Based Adaptive Noise Cancelling System", Proc. of the 12th Int. Conference on Digital Audio Effects (DAFx-09), Como, Italy, September 1-4, 2009.

- [8] Jerin K., "FPGA implementation of adaptive noise cancellation", Master Thesis, Electronics and Communication Engineering, University of Kerala, 2012.

- [9] David A., "Real time digital signal processing: Adaptive filters for correlated noise reduction in ring laser gyro inertial systems", Master Thesis, Department of Electrical Engineering, College of Engineering, University of South Florida, 2004.

- [10] Sen M., Issa P., Kai M., Tom H, Mark N., and Jason C., "Design of active noise control systems with the TMS320 family".

- [11] Ali A., Hamza A., and Mohamed F., "Robust Automatic Speech recognition System Implemented in a Hybrid Design DSP-FPGA", International Journal of

Signal Processing, Image Processing and Pattern Recognition Vol.6, No.5, 2013, pp.333-342, http://dx.doi.org/10.14257/ijsip.2013.6.5.29.

- [12] Simon H.," Least-Mean-Square Adaptive Filters", A John Wiley & Sons, Inc. Publication, 2003.

- [13] Joseph G., "Adaptive Filter Architectures for FPGA Implementation", Master Thesis, Department of Electrical and Computer Engineering, Florida State University, 2004.